August 29, 2022

August 29, 2022

Categories

Thank you very much for tuning into our first blogpost! To explain the origin story of LUBIS EDA`s, we need to take a small trip back to […]

August 29, 2022

August 29, 2022

Categories

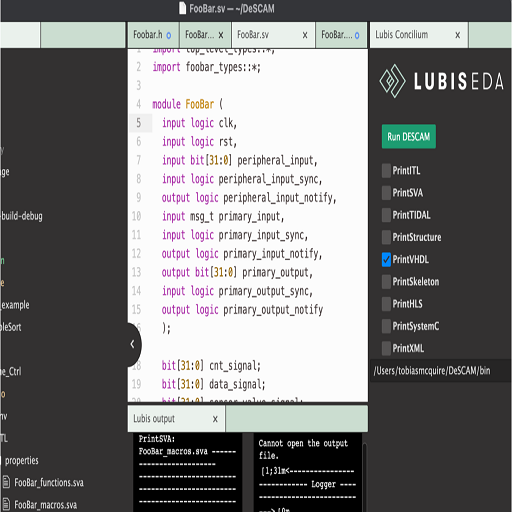

Within this series we keep you updated on our mission to provide you tools for your Agile Hardware Development! LUBIS IDE is coming:The time of error […]

August 29, 2022

August 29, 2022

Categories

In the world of software development many companies have switched to agile design methods, achieving a faster time to market, fewer bugs and an increased ROI […]

August 29, 2022

August 29, 2022

Categories

Within this series we at LUBIS EDA keep you updated on our mission to provide you tools for your Agile Hardware Development! LUBIS IDE is here: We […]

August 29, 2022

August 29, 2022

Categories

Today, formal verification is mostly used for bug hunting. Writing formal properties is time consuming and requires a certain level of expertise. The performance of formal […]

August 29, 2022

August 29, 2022

Categories

At LUBIS EDA, Summer is coming! We used the time before the easter break for a spring-clean.We worked on our code base to set our selfs […]

August 29, 2022

August 29, 2022

Categories

The recent Wilson Research Group Functional Verification Study analyzed how verification nowadays influences the way ASIC/IC projects are managed. The numbers indicate that companies spent a majority of time and […]

August 29, 2022

August 29, 2022

Categories

For us it’s time to spice up our secret sauce! Improved Verification IP generation: We aim to reduce the properties to a bare minimum by removing any […]

August 29, 2022

August 29, 2022

Categories

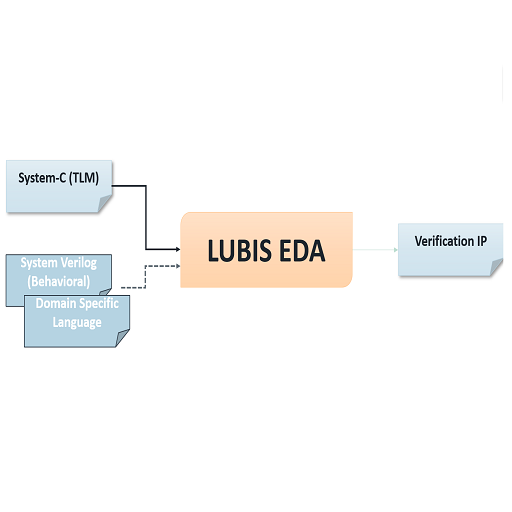

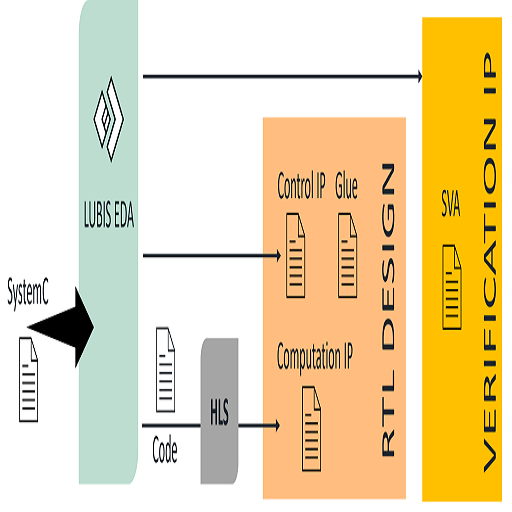

LUBIS EDA works on a novel solution to generate a synthesizable hardware design from an abstract software model. Our goal is to enhance conventional High-Level Synthesis (HLS) flows by […]