#4 WHAT’S THE NEWS? – KEEP UP TO DATE!

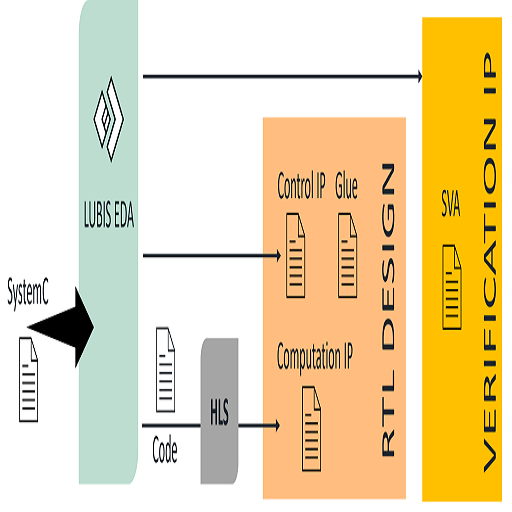

August 29, 2022LUBIS EDA works on a novel solution to generate a synthesizable hardware design from an abstract software model. Our goal is to enhance conventional High-Level Synthesis (HLS) flows by making it suitable for control-oriented designs (e.g., controllers or a bus). As shown in in the figure above, our flow starts with a SystemC model that is analyzed and then, based on the model, we generate a:

- RTL DESIGN IP: The automatically generated Design IP consists of a Control IP and a Computation IP. The components are connected with a special glue logic. Our solution generates a code that instruments standard HLS solutions to generate the Computation IP. The Control IP is directly generated from the parsed SystemC models.

- VERIFICATION IP: The Verification IP is composed of SVA properties that are used to verify that the generated design is bug-free. The properties allow designer to manually optimize the design while ensuring correct functional behavior. The properties are easy to read, fast to prove and completely cover the entire functional behavior of the design.

What’s new?

- We improve traditional High-Level Synthesis (HLS) flows by making them suitable for control-oriented designs.

- We provide a formal verification IP allowing designers to alter the design according to their needs.

- We guarantee a bug-free design with respect to the SystemC model.

- We can provide a trustable and sound high-level power estimation.

Are you interested? Reach out to us for more details!

Check out how easily it fits in your flow:

https://www.youtube.com/watch?v=csADrObTFec&t=15s

Follow us on LinkedIn for more updates:

https://www.linkedin.com/company/lubis-eda

Kind regards,

Tobias Ludwig

CEO & Founder

LinkedIn Profile