#4 WHAT’S THE NEWS? – KEEP UP TO DATE!

August 29, 2022

#3 WHAT’S THE NEWS? – KEEP UP TO DATE!

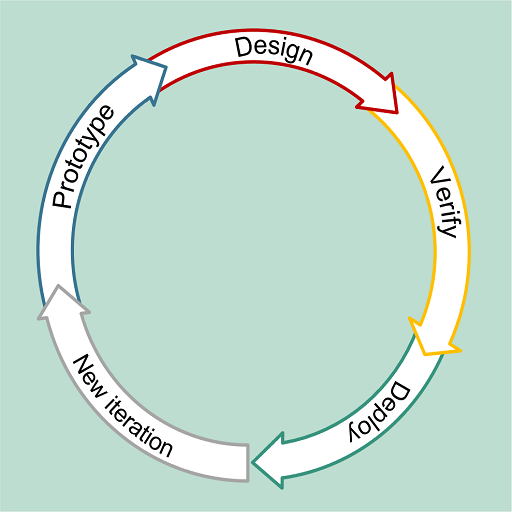

August 29, 2022The recent Wilson Research Group Functional Verification Study analyzed how verification nowadays influences the way ASIC/IC projects are managed. The numbers indicate that companies spent a majority of time and resources on IC verification. Verification Engineers spend 41% of their time debugging bugs. Half of those bugs can be classified as functional or logic flaws. 68% of the project require at least one re-spin. This doesn`t have to be the case! We, as LUBIS EDA, will show you how to avoid costly re-spins in ASIC/IC projects by using formal verification early in the process.

Does your company have:

- Increasing costs due to longer project times.

- Less revenue due to later Time-To-Market (TTM).

With our solution, we can ease that pain by:

- Automatically generating a Verification IP (VIP) out of your specifications.

- The VIP is composed of formal properties (SVA format) that cover the complete functional range, as described within the specification.

- Use the VIP early on within the process, find functional bugs early on and save debugging / verification resources.

- Proving the VIP means, that your design is correct-by-construction w.r.t your spec.

- Avoid re-spins, shorten your TTM and save development costs.

For more information about the automatic VIP generation, check out:

Let us democratise formal property generation

Interested? Questions? Concerned?

Please feel free to contact us!

We are happy to hear from you!